# Lecture 10: Circuit Families

#### Outline

- Pseudo-nMOS Logic

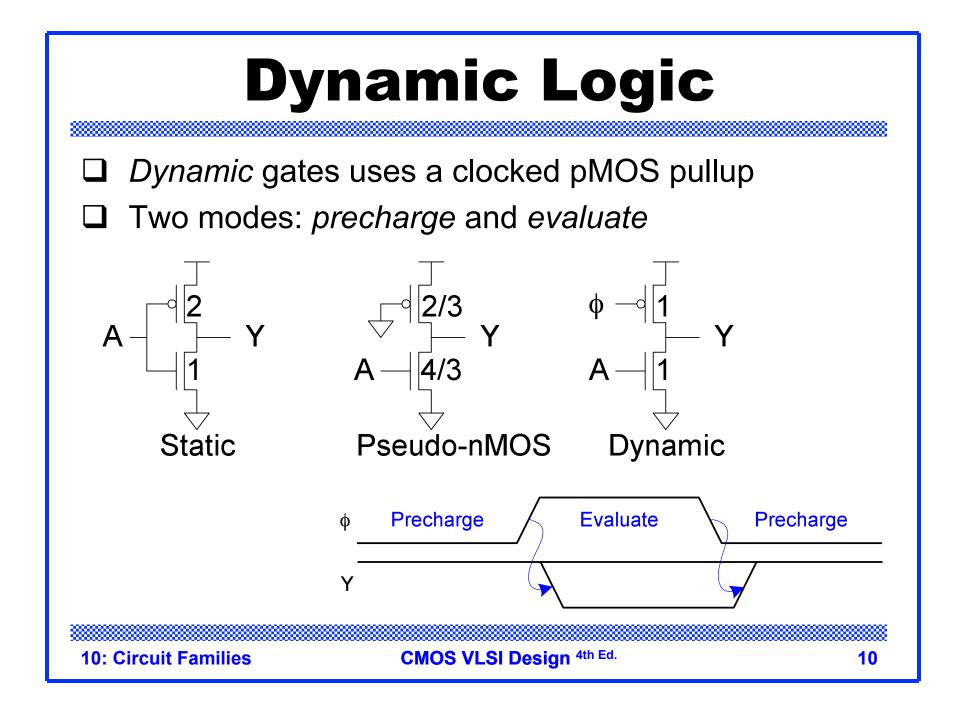

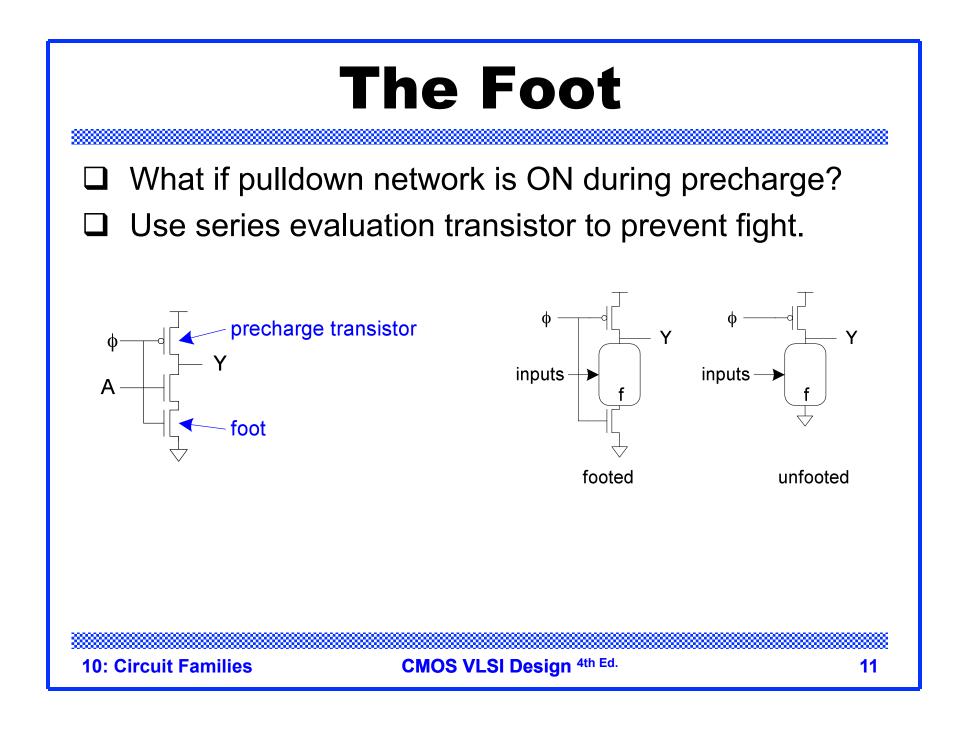

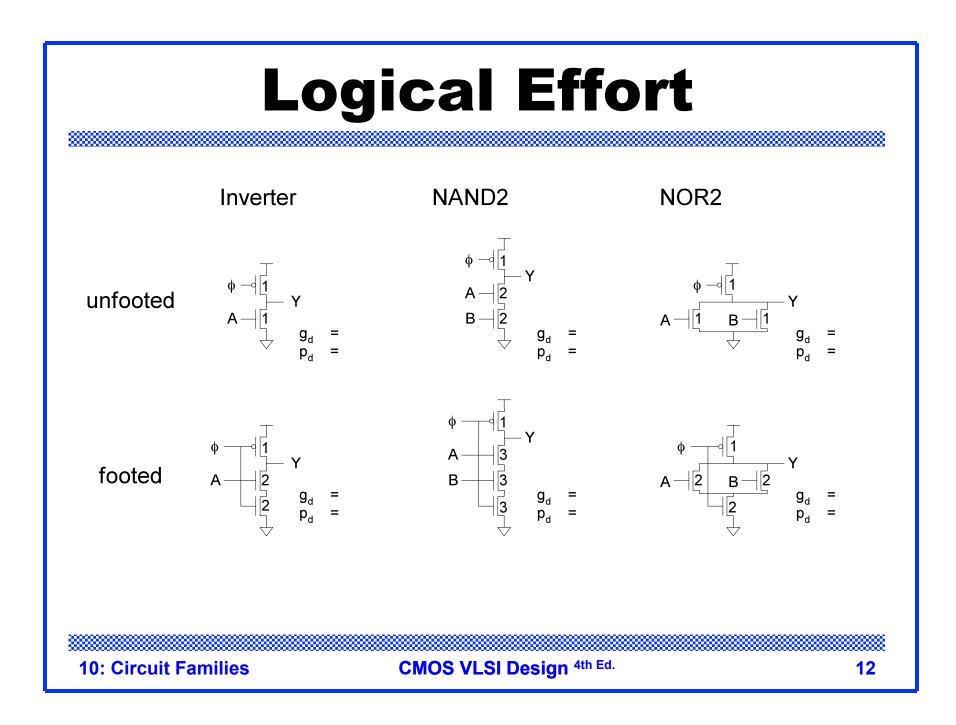

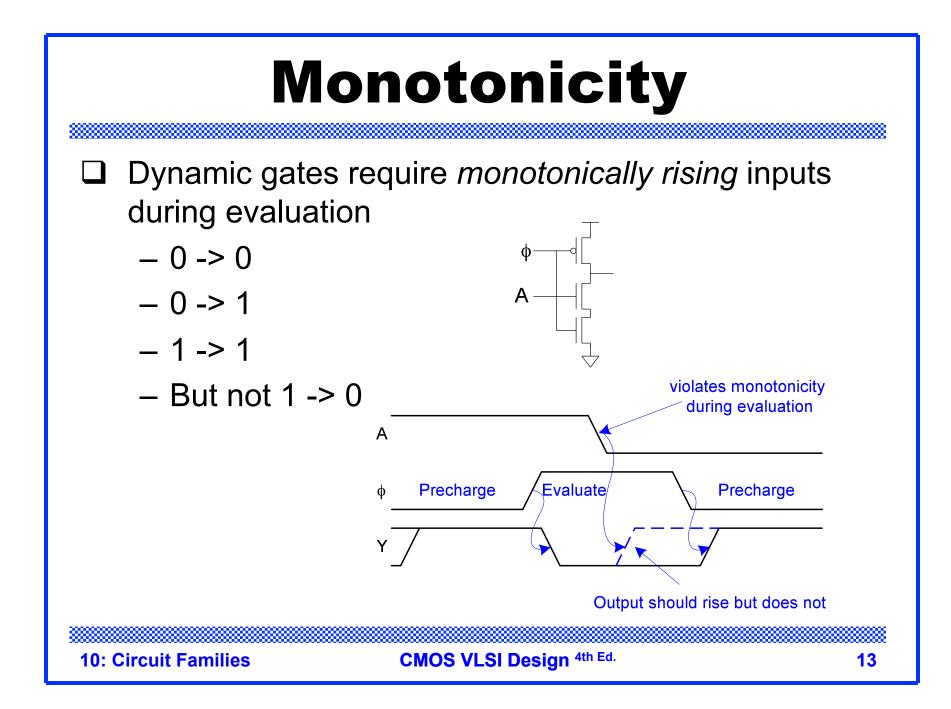

- Dynamic Logic

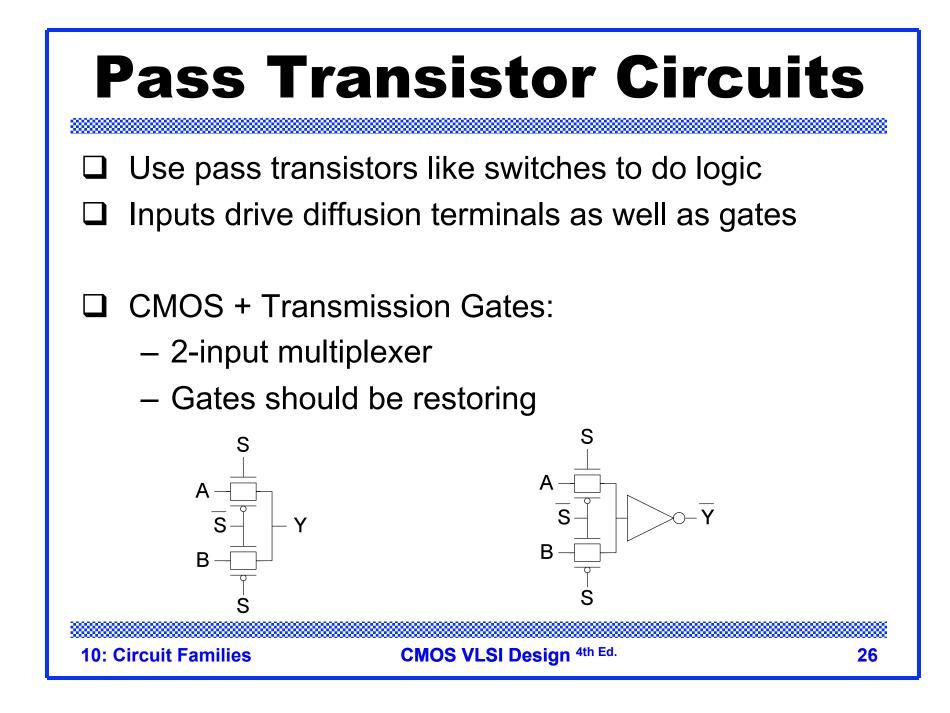

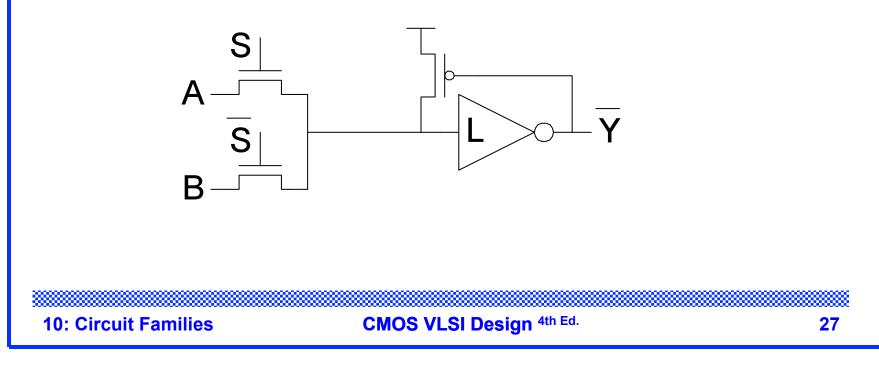

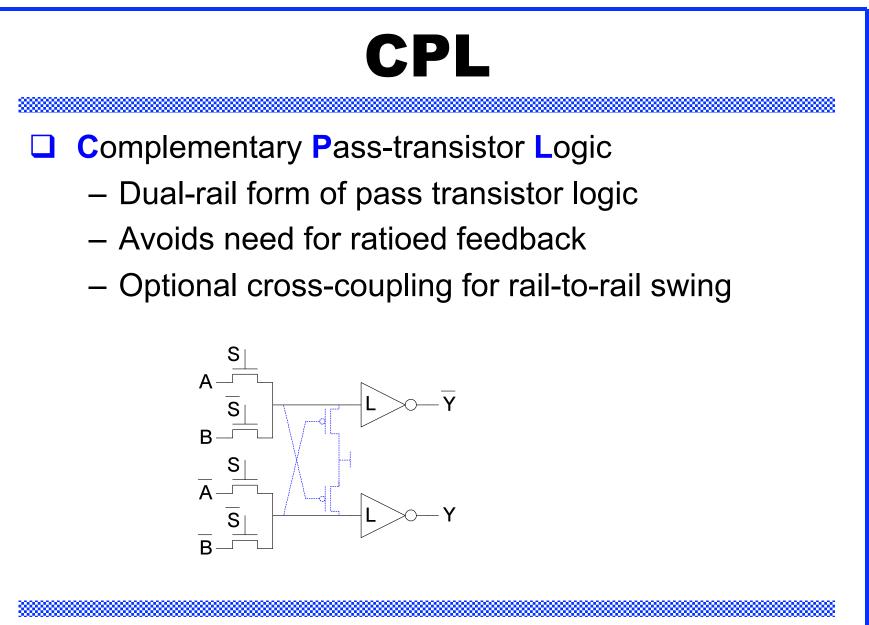

- Pass Transistor Logic

CMOS VLSI Design <sup>4th Ed.</sup>

#### Introduction

❑ What makes a circuit fast?

- -I = C dV/dt ->  $t_{pd} \propto (C/I) \Delta V$

- low capacitance

- high current

- small swing

- □ Logical effort is proportional to C/I

- ☐ pMOS are the enemy!

- High capacitance for a given current

- □ Can we take the pMOS capacitance off the input?

- ❑ Various circuit families try to do this...

CMOS VLSI Design 4th Ed.

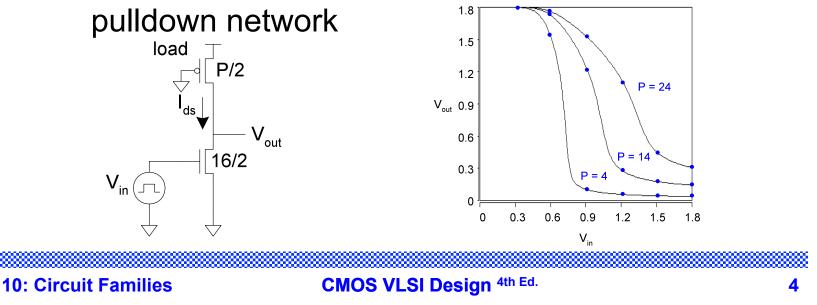

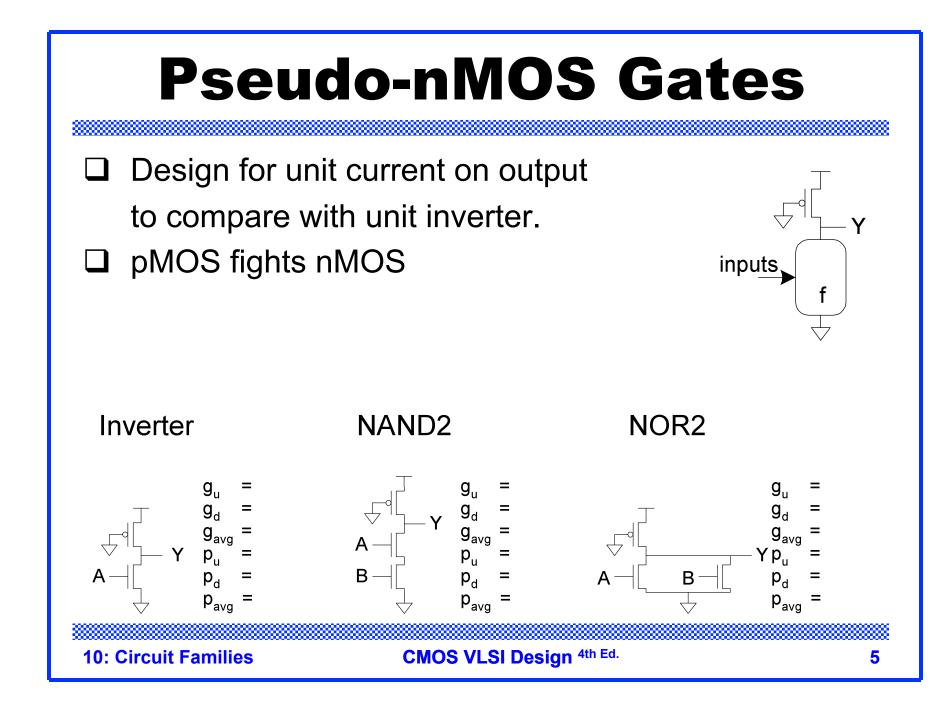

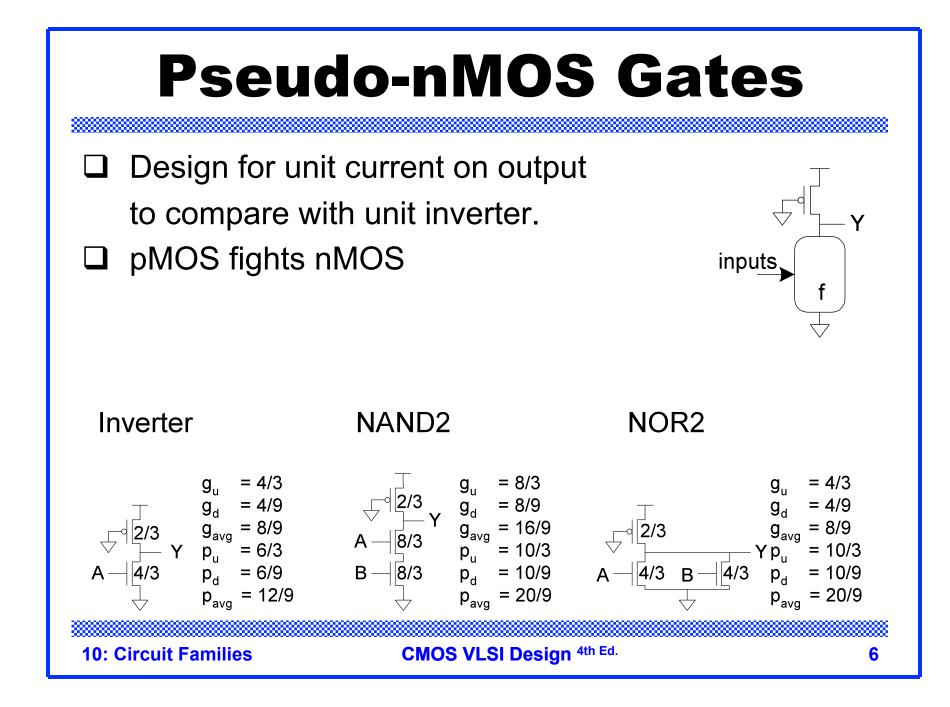

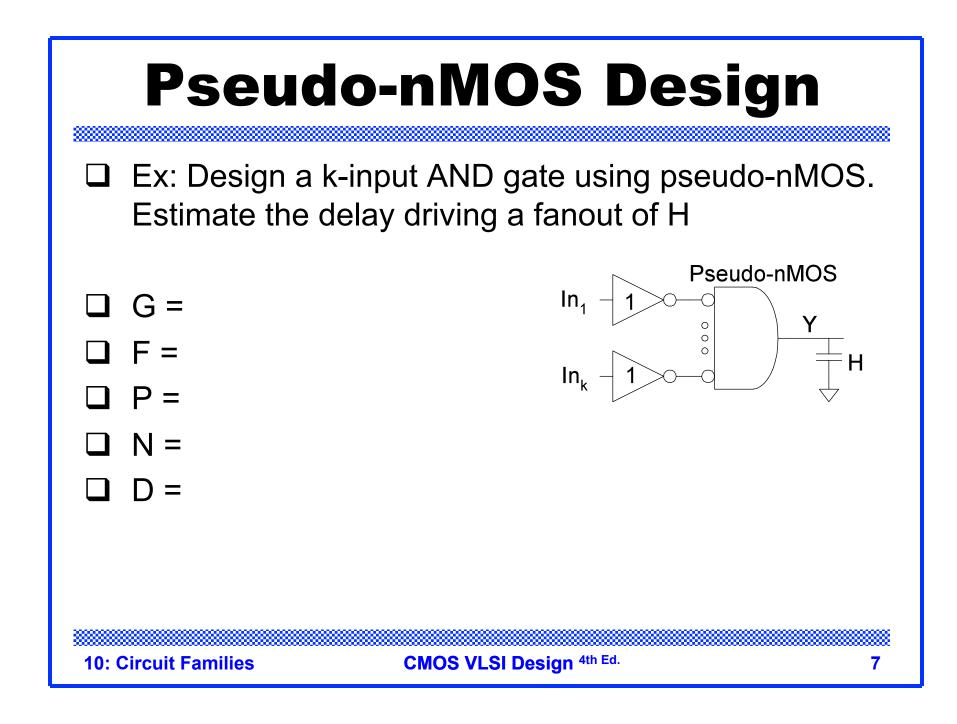

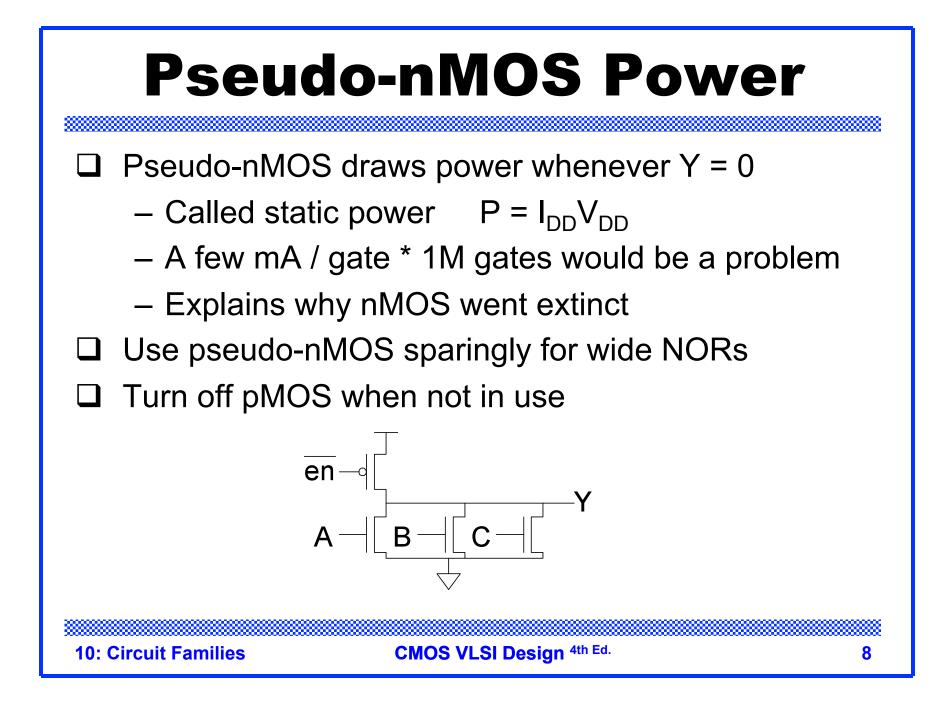

#### **Pseudo-nMOS**

In the old days, nMOS processes had no pMOS

- Instead, use pull-up transistor that is always ON

- □ In CMOS, use a pMOS that is always ON

- Ratio issue

- Make pMOS about ¼ effective strength of

#### **Ratio Example**

☐ The chip contains a 32 word x 48 bit ROM

- Uses pseudo-nMOS decoder and bitline pullups

- On average, one wordline and 24 bitlines are high

□ Find static power drawn by the ROM

$$-I_{on-p} = 36 \ \mu A, V_{DD} = 1.0 \ V$$

#### **Solution**:

$$P_{\text{pull-up}} =$$

$P_{\text{static}} =$

**10: Circuit Families**

#### CMOS VLSI Design <sup>4th Ed.</sup>

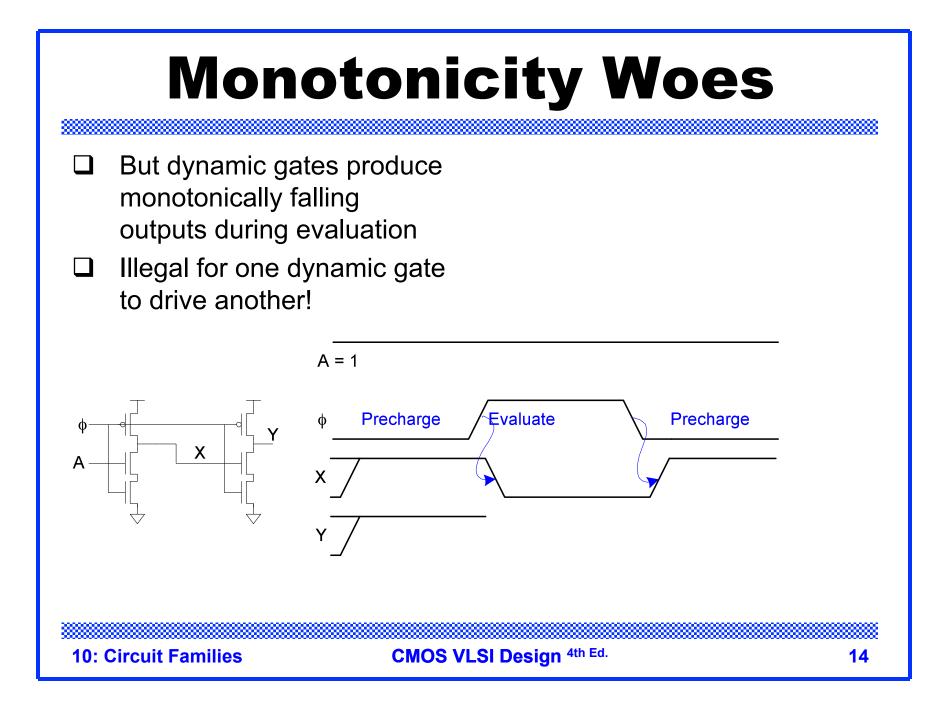

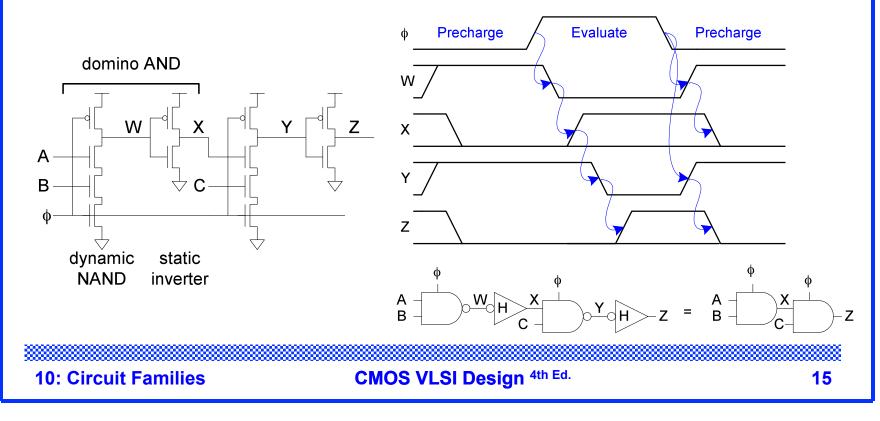

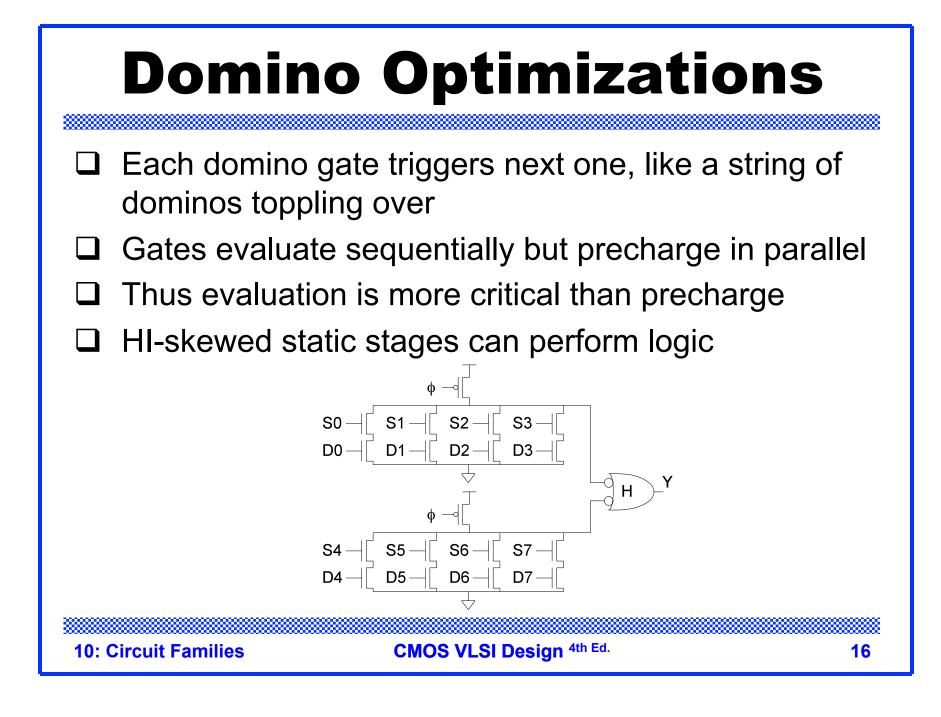

#### **Domino Gates**

Follow dynamic stage with inverting static gate

- Dynamic / static pair is called domino gate

- Produces monotonic outputs

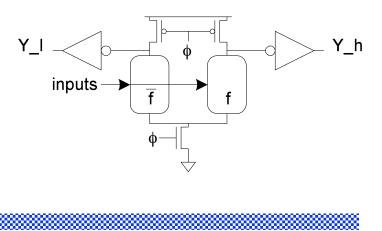

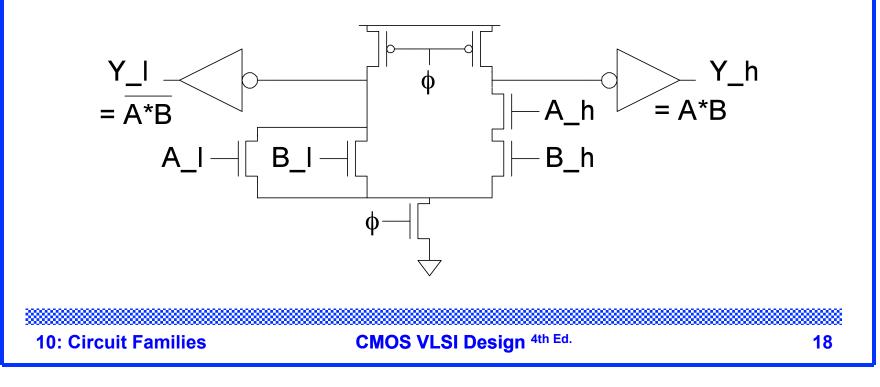

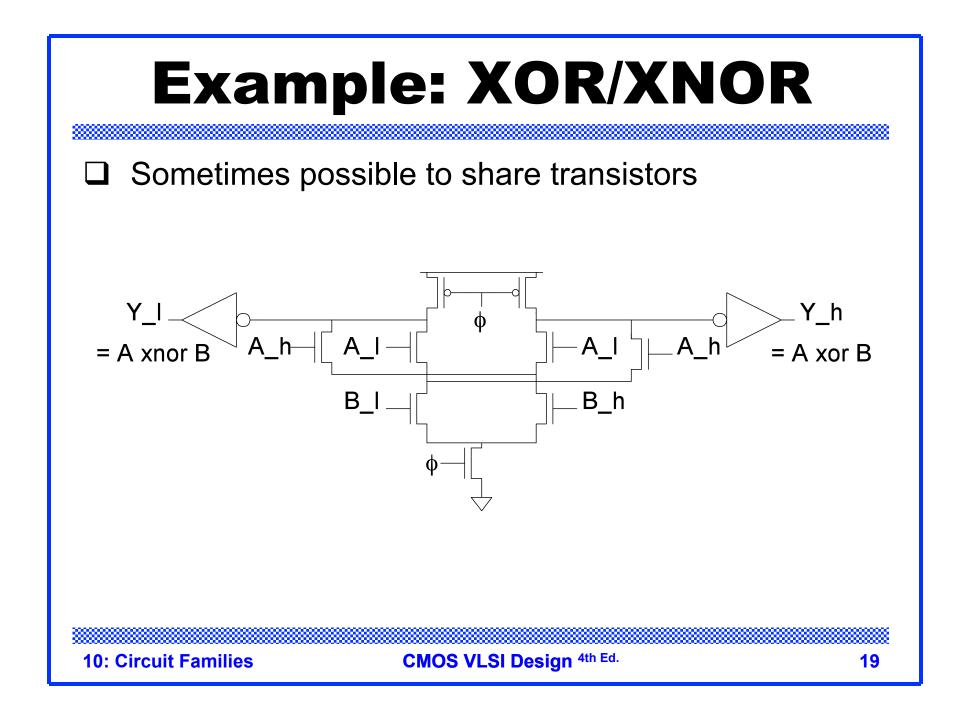

# **Dual-Rail Domino**

Domino only performs noninverting functions:

- AND, OR but not NAND, NOR, or XOR

- Dual-rail domino solves this problem

- Takes true and complementary inputs

- Produces true and complementary outputs

| sig_h | sig_l | Meaning    |

|-------|-------|------------|

| 0     | 0     | Precharged |

| 0     | 1     | '0'        |

| 1     | 0     | '1'        |

| 1     | 1     | invalid    |

**10: Circuit Families**

CMOS VLSI Design 4th Ed.

- Given A\_h, A\_I, B\_h, B\_I

- **Compute Y\_h = AB, Y\_I = \overline{AB}**

- Pulldown networks are conduction complements

# **Noise Sensitivity**

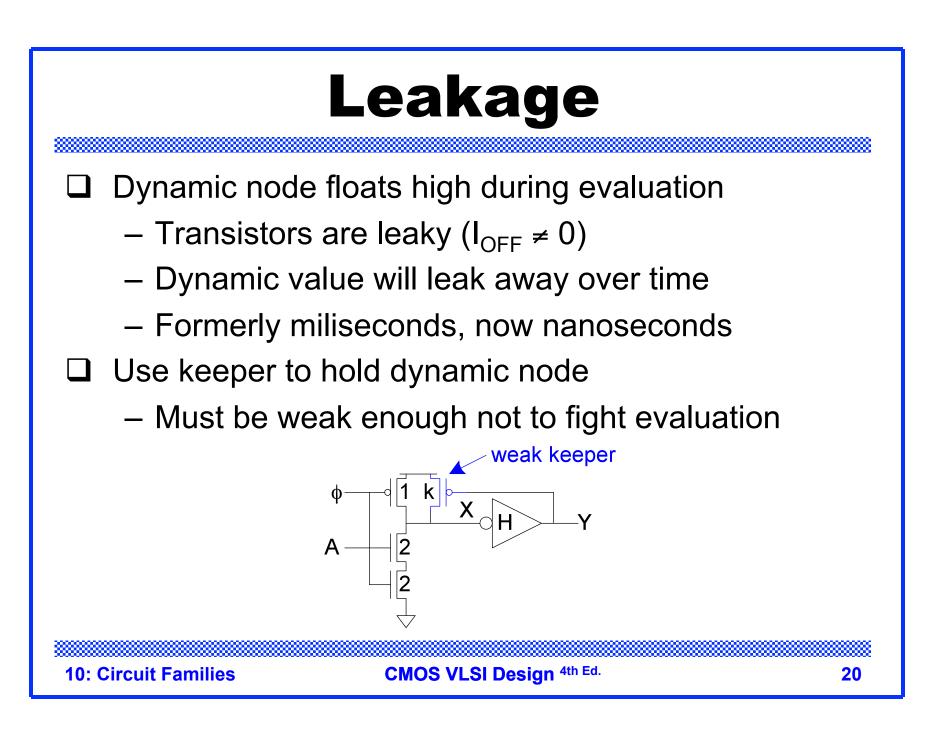

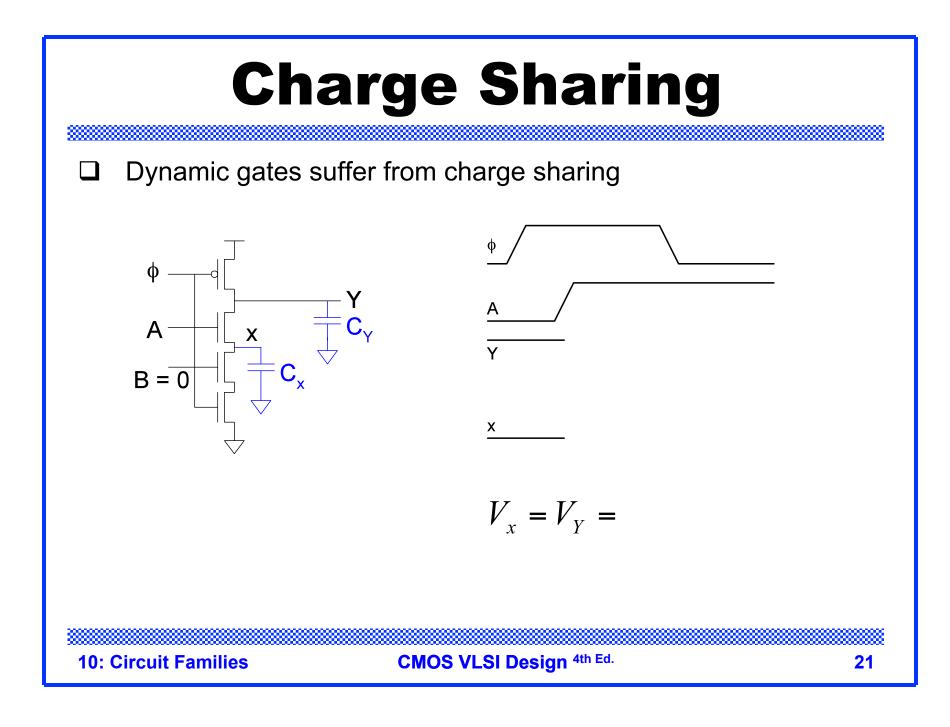

Dynamic gates are very sensitive to noise

- Inputs:  $V_{IH} \approx V_{tn}$

- Outputs: floating output susceptible noise

Noise sources

- Capacitive crosstalk

- Charge sharing

- Power supply noise

- Feedthrough noise

- And more!

#### Power Domino gates have high activity factors Output evaluates and precharges • If output probability = 0.5, $\alpha$ = 0.5 Output rises and falls on half the cycles – Clocked transistors have $\alpha = 1$ Leads to very high power consumption **10: Circuit Families** CMOS VLSI Design 4th Ed. 24

# **Domino Summary**

- Domino logic is attractive for high-speed circuits

- -1.3 2x faster than static CMOS

- But many challenges:

- Monotonicity, leakage, charge sharing, noise

- Widely used in high-performance microprocessors in 1990s when speed was king

- Largely displaced by static CMOS now that power is the limiter

- □ Still used in memories for area efficiency

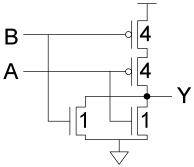

#### LEAP

- □ LEAn integration with Pass transistors

- Get rid of pMOS transistors

- Use weak pMOS feedback to pull fully high

- Ratio constraint

**10: Circuit Families**

CMOS VLSI Design <sup>4th Ed.</sup>