# 55:131 Introduction to VLSI Design

#### Flash and DRAM

Adapted from Weste and Harris notes except as noted Flash and DRAM sections adapted from "Digital Integrated Circuits", copyright 2003 Prentice Hall/ Pearson

## Outline

- Memory Arrays

- Flash

- DRAM

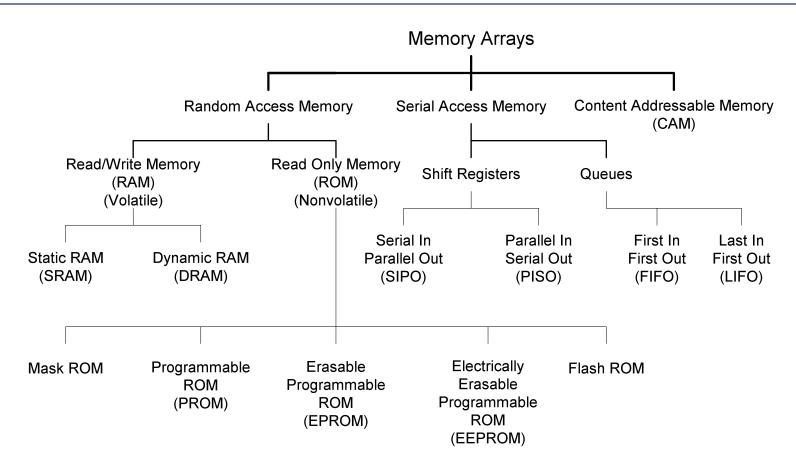

# Memory Arrays

## Array Architecture

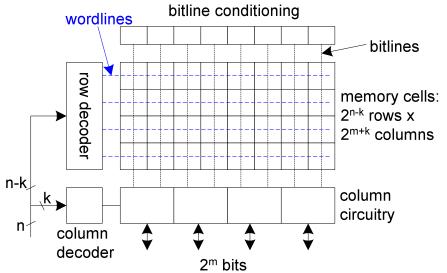

- 2<sup>n</sup> words of 2<sup>m</sup> bits each

- If n >> m, fold by 2<sup>k</sup> into fewer rows of more columns

- Good regularity easy to design

- Very high density if good cells are used

#### Non-Volatile Memories

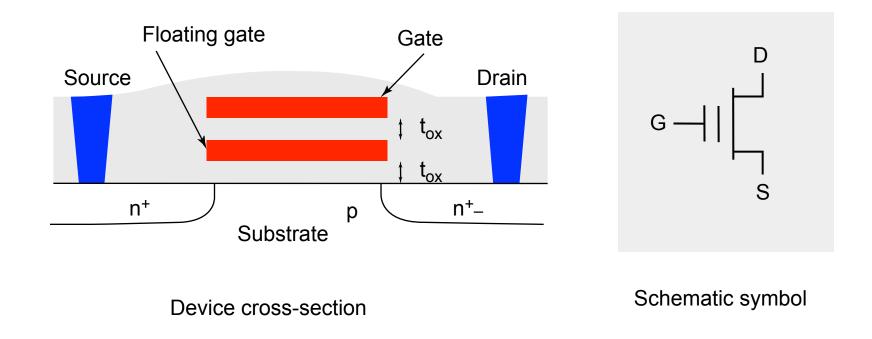

#### Floating-gate transistor

#### Floating-Gate Transistor Programming

| 0 V     | 20 V             | 20 V      | 20 V              | 10 V               |

|---------|------------------|-----------|-------------------|--------------------|

| _ل_     |                  | <u> </u>  | <u> </u>          |                    |

| <u></u> | 兲                | 0 \ 0 \   | 8 V J ~ 8 V       | ذ ب_ر ذ            |

| 20 V    | 20 V             | 0 V       | 0 V               | 0 V                |

| Erase   | Inhibit<br>Erase | Program 0 | Do Not<br>Program | Inhibit<br>Program |

FN Tunneling Remove e-Negative Vt "1" FN Tunneling Add e-Positive Vt "0"

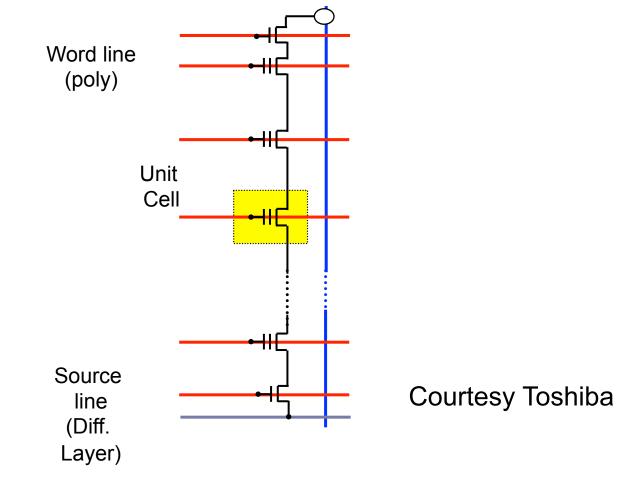

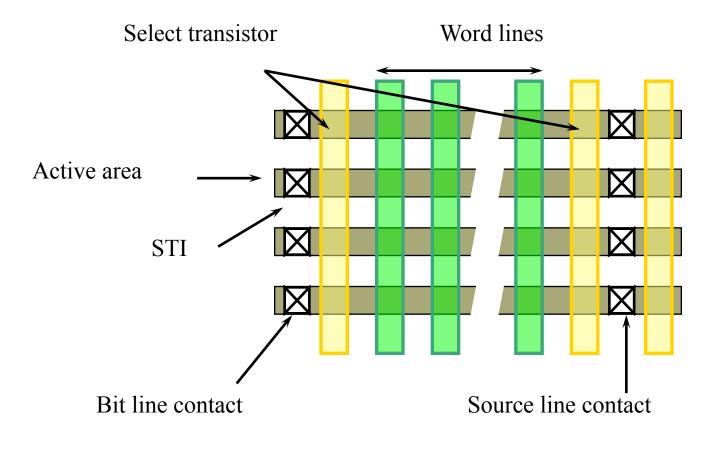

### NAND Flash Memory

# NAND Flash Memory

# Read-Write Memories (RAM)

#### Static (SRAM)

- Data stored as long as supply is applied

- Large (6 transistors/cell)

- Fast

- Differential

- Dynamic (DRAM)

- Periodic refresh required

- Small (1-3 transistors/cell)

- Slower

- Single Ended

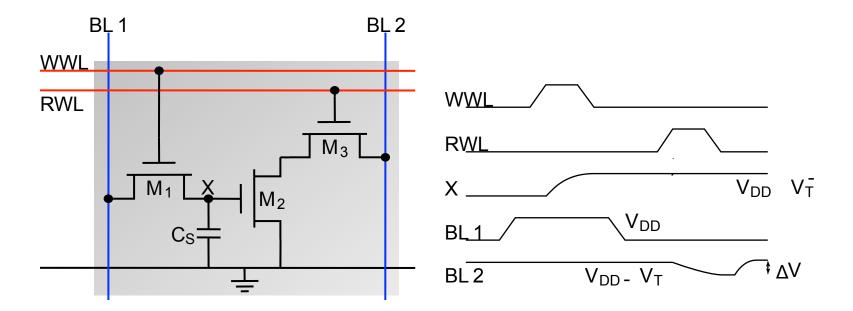

#### 3-Transistor DRAM Cell

- No constraints on device ratios

- Reads are non-destructive

- Value stored at node X when writing a "1" = V<sub>wwl</sub>-V<sub>tn</sub>

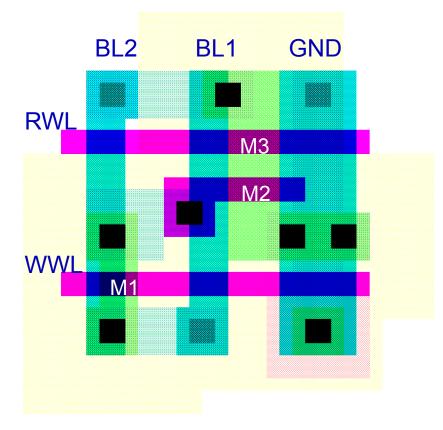

#### 3T-DRAM — Layout

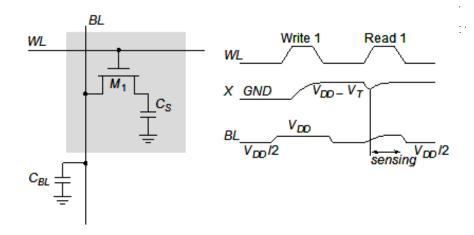

## 1-Transistor DRAM Cell

- Write: Cs is charged or discharged by asserting WL and BL

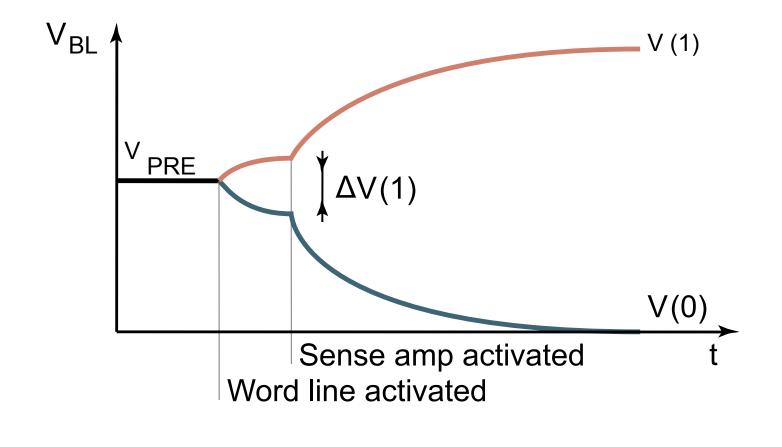

- Read: Charge redistribution takes place between bit line and storage capacitance

- Voltage swing is small; typically around 250 mV

# **DRAM Cell Observations**

- IT DRAM requires a sense amplifier for each bit line, due to charge redistribution read-out.

- DRAM memory cells are single ended in contrast to SRAM cells.

- The read-out of the 1T DRAM cell is destructive; read and refresh operations are necessary for correct operation.

- Unlike 3T cell, 1T cell requires presence of an extra capacitance that must be explicitly included in the design.

- When writing a "1" into a DRAM cell, a threshold voltage is lost. This charge loss can be circumvented by bootstrapping the word lines to a higher value than V<sub>DD</sub>

#### Sense Amp Operation

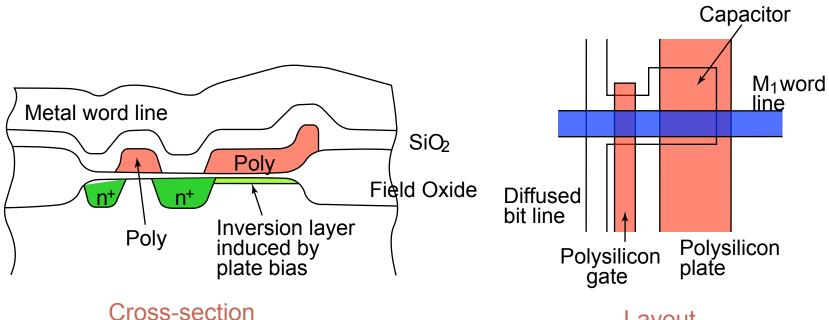

# 1-T DRAM Cell

Layout

#### **Uses Polysilicon-Diffusion Capacitance Expensive in Area**

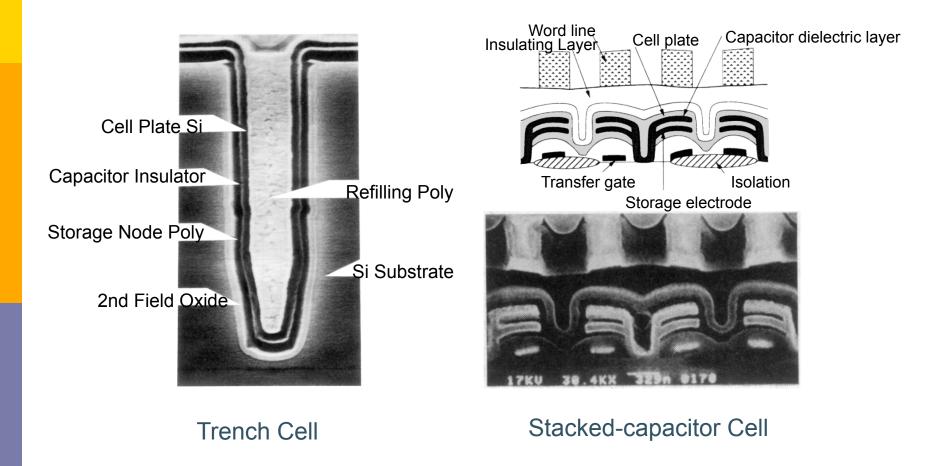

# Advanced 1T DRAM Cells

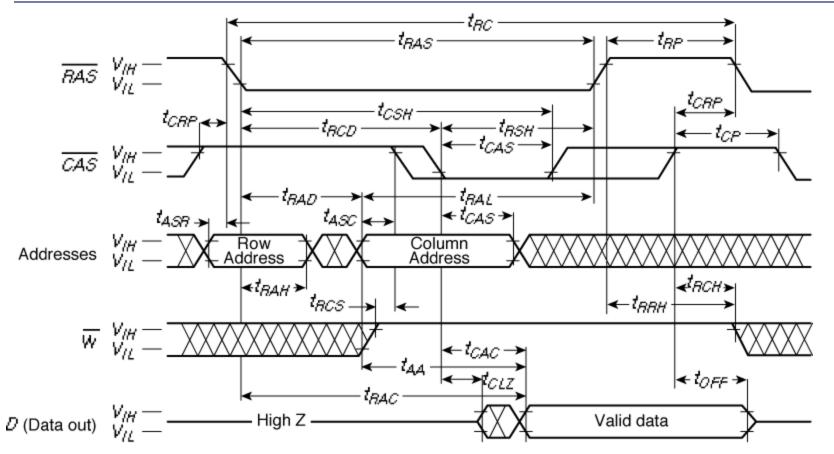

## **DRAM** Timing

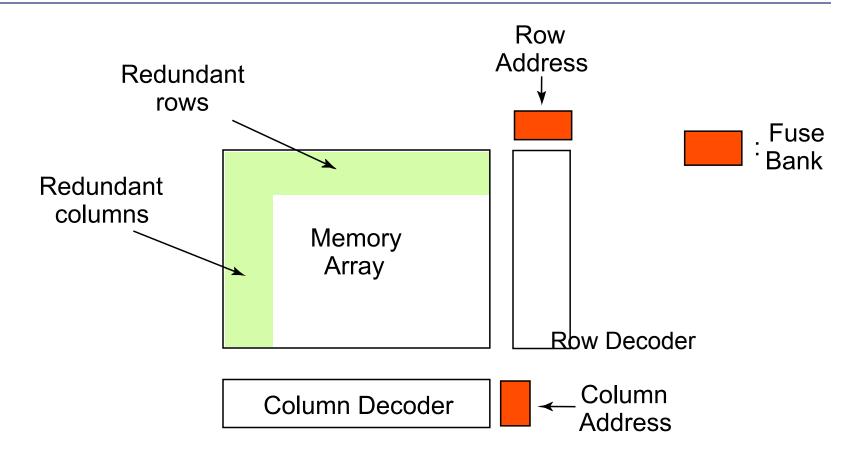

# Redundancy