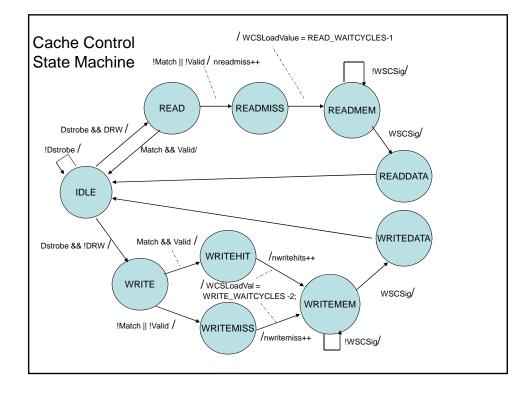

## Cache Controller--States

- IDLE: no memory access underway

- READ: Read access initiated by driver; Cache is checked during this state. If hit, access is satisfied from cache during this cycle and control returns to IDLE state at next transition. If miss, transition to READMISS state to initiate main memory access

- READMISS: Initiate memory access following a read miss. Wait state counter is loaded to time the wait for completion of the main memory access. Transition to READMEM State.

- READMEM: Main memory read in progress. Remain in this state until wait state counter expires then transition to READDATA state. (Main memory read requires READ\_WAITCYCLES cycles to complete)

- READDATA: Data available from main memory read. Write this data into the cache line and use it to satisfy the original processor (driver) read request

## Cache Control—Signals Asserted

- IDLE: none

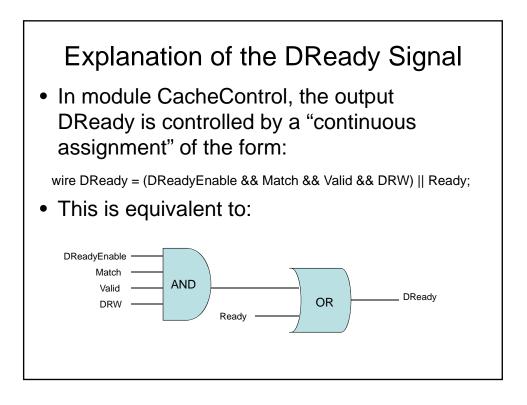

- READ: DReadyEnable, DDataOE, Hit (if read hit)

- READMISS: Miss, WSCLoad, MStrobe, MRW, DDataOE

- READMEM: MRW, DDataOE

- READDATA: Ready, Write, MRW, CacheDataSelect, DDataSelect, DDataOE

- WRITE:

- WRITEHIT: Hit, WSCLoad, Write, MStrobe, MDataOE

- WRITEMISS: Miss, WSCLoad, Write, MStrobe, MDataOE

- WRITEMEM: MDataOE

- WRITEDATA: Ready, MDataOE

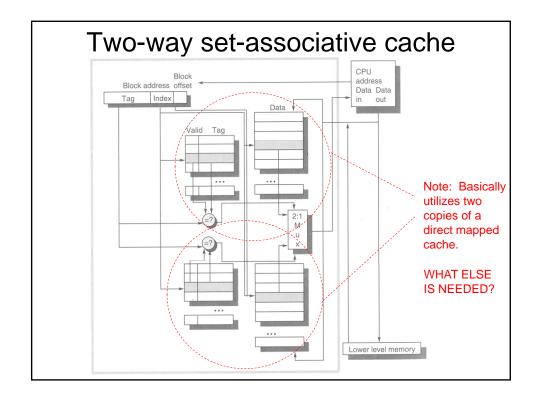

Note: Signals **Hit** and **Miss** are not shown on the diagrams or used in the implementation of the direct mapped cache. These signals may aid in the implementation of the set-associative cache